# 2025 IEEE CICC Review

고려대학교 전기및전자공학부 박사과정 안재웅

## **Session 2 Analog Building Blocks and Sensing Circuits**

이번 2025 CICC의 Session 2에서는 analog building blocks and sensing circuits라는 주제로 총 5편의 논문이 발표되었다. 이 중 #2-1은 mixed-signal 구조를 활용한 고속·저잡음 current sensing 회로를 제안하였으며, #2-3은 high input impedance와 flicker noise reduction을 동시에 달성한 뇌파 측정용 증폭기를 발표하였다. 또한 #2-5는 배터리 상태 진단이 가능한 고정밀 AFE를 구현하였다.

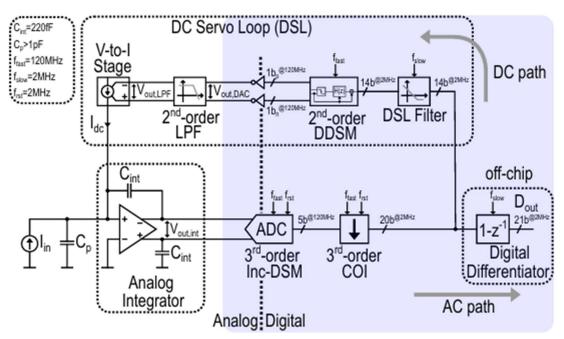

#2-1 논문은 low noise와 high throughput을 동시에 만족하는 current sensing을 위해 mixed-signal integrator-differentiator TIA(MS-TIA)를 제안하였다. 기존 analog I-D-TIA는 integrator로 낮은 노이즈를 확보하고 differentiator로 고속 처리를 달성하지만, 아날로그 differentiator는 고속 동작을 위한 대형 커패시터와 높은 전력 소모, 면적 부담 등 구조적 한계를 지닌다. 본 논문은 이러한 한계를 극복하고자, differentiator와 DC servo loop (DSL)를 디지털 블록으로 대체하여 주요 신호 처리를 디지털 도메인으로 이전함으로써 공정 이점을 극대화하고 설계 유연성과 확장성을 확보하였다. 입력 전류는 아날로그 integrator에서 적분된 후, 3차 incremental delta-sigma modulator와 COI 필터를 통해 직접 디지털화되며, 디지털 differentiator를 통해 AC 성분을 분리하고, 디지털 DSL 필터와 2차 digital DSM을 통해 DC feedback을 구현한다. 또한 아날로그 영역에서는 chopper 방식의 voltage to current converter와 2차 아날로그 low pass filter를 통해 정밀한 DC current feedback을 제공한다. 실측 결과, floating input 기준 최소 spot noise는 22fA√Hz, DC bias ±12nA 조건에서도 28fA/√Hz로 유지되었으며, 1MHz bandwidth에서 통합 노이즈는 131pArms에 달했다. 입력 주파수에 따라 동적 범위가 달라지며, -6dBFS 기준 800kHz 입력에서 SNDR 58.2dB, SFDR 64.0dB의 성능을 기록하였다.

[그림 1] #2-1에서 제시한 mixed signal integrator-differentiator TIA

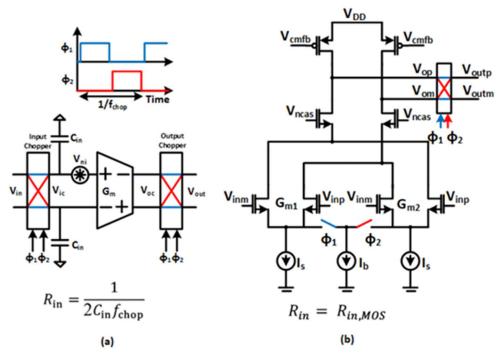

#2-3 논문은 neural recording 응용을 위한 high input impedence를 가지는 buffer amplifier를 제안하였다. 기존의 chopper-stabilized amplifier는 flicker noise를 효과적으로 억제할 수 있으나, 입력단 스위칭에 의해 input impedance가 수십  $M\Omega$  수준으로 낮아져 high impedance 소스와의 연결 시 신호 감쇠가 발생하는 문제가 있다. 본 논문에서는 이러한 문제를 해결하기 위해, 입력단에 스위치를 도입하지 않고 tail current에 chopping을 적용하는 bias chopping 기법을 제안하였다. 이 방식은 입력 MOS 트랜지스터 자체의 임 피던스를 그대로 유지하면서도, 신호를 chopping 주파수로 변조하여 flicker noise를 상위대역으로 이동시키고 저역에서 제거할 수 있도록 한다. 실측 결과, 입력 임피던스는 최대  $20G\Omega$ , 평균  $16.7G\Omega$ 으로 측정되었으며, conventional chopping 대비 최대 9dB, 평균 약 8dB 수준의 SNR 개선이 확인되었다. 특히 source impedance가 높은 조건에서 conventional 방식 대비 신호 감쇠가 크게 줄어들어 실제 응용 환경에서 실질적인 SNR 이 더 향상되는 효과가 입증되었다. 또한 전체 회로는 0.003mm²의 초소형 면적과  $64\mu$ W 의 소비전력을 가진다.

[그림 2] (a) 기존의 chopping 방식과 (b) 제안하는 chopping 방식

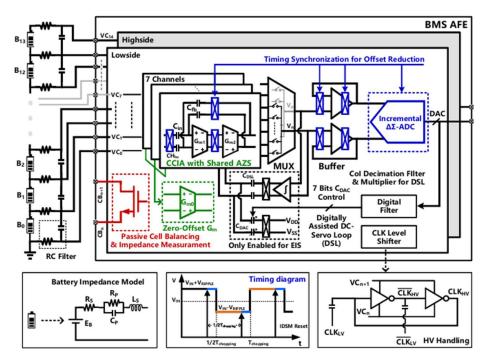

#2-5 논문은 총 14셀의 리튬이온 배터리를 모니터링할 수 있는 AFE를 제안하였다. 본 회로는 배터리 전압 측정 정확도를 극대화하기 위해 1mV 이내의 Total Measurement Error를 달성하였으며, 동시에 Electrochemical Impedance Spectroscopy (EIS)기능을 통합 하여 State of Health까지 가능한 점이 큰 특징이다. AFE의 핵심 증폭기는 capacitivelycoupled chopper instrumentation amplifier (CCIA) 기반이며, 여기에 채널 공유형 autozero stabilization (AZS) 경로를 도입하여 입력 offset을 억제하고, chopping 동기화를 통 해 출력 ripple을 디지털 필터 레벨에서 제거함으로써 추가적인 아날로그 회로 없이 높 은 정확도를 확보하였다. AZS 경로는 7개의 채널이 순차적으로 공유하며, 면적과 전력 측면 모두에서 효율적이다. EIS 기능은 기존의 패시브 셀 밸런싱 회로를 그대로 재활용하 여 구현되었으며, 외부 회로 추가 없이 1-bit delta-sigma 방식의 bit-stream current IP를 주입하고, 배터리 양단 전압 응답을 통해 실시간 임피던스를 추정한다. EIS 동작 중에는 coarse/fine DC servo loop을 순차적으로 적용하여 대용량 DC 성분을 제거하고, 이에 따 라 3Hz에서 2kHz까지의 주파수 대역과 0.2mΩ 수준의 임피던스 분해능을 확보하였다. 또한 incremental delta-sigma ADC의 내부 동작을 활용해 chopping에 의해 유입되는 ripple 성분을 디지털 필터 가중치 비대칭을 통해 자연스럽게 상쇄함으로써, 회로 복잡도 증가 없이 ripple-free 출력을 얻는 기법도 함께 제안되었다. 회로는 0.18µm BCD 공정으 로 구현되었으며, 12.5mm² 면적과 2.3mA@5V의 저전력으로 구동된다. 실측 결과, -40℃

에서 85°C에 이르는 넓은 온도 범위에서도 70채널 모두 TME가 1mV 이내로 유지되었고, AZS 및 chopping 동기화 적용 시 출력 ripple은 0.1mV까지 억제되었다.

[그림 3] #2-5 논문에서 BMS AFE 구조

### 저자정보

## 안재웅 박사과정 대학원생

● 소속 : 고려대학교

● 연구분야 : 디스플레이 드라이버 / 픽셀 보상 / 터치 센서

• 이메일 : ajw1104@korea.ac.kr

• 홈페이지 : https://sites.google.com/site/kubasiclab/home

# 2025 IEEE CICC Review

KAIST 전기및전자공학부 박사과정 박수언

# Session 12 Advancements in Low-Power, High-Performance Analog Sensing and Interface Technologies

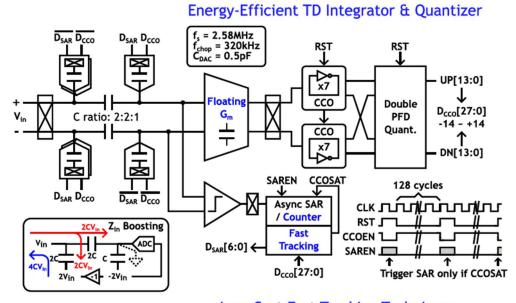

#12-2 는 Peking 대학에서 발표된 논문으로, IoT, 의료, wearable 등에 사용되는 energy efficient한 CT-based의 tracking-zoom sensor 구조를 발표하였다. 제안하는 구조는 높은 해상도와 에너지 효율성을 모두 갖기 위해 zoom architecture를 채택하였으며, ΔΣ loop이 artifacts에 의해 saturation되는 경우 asynchronous SAR이 동작하여 효율적으로 빠른 recovery 수행한다. Fine-quantization을 위한 CCO를 current-reuse 특성을 갖는 floating domain에서 구현하여 energy efficiency를 더욱 증가시킨 점이 차별화된 특징이다. Capacitive DAC의 matching을 위해 SAR과 CCO DAC을 layout에서 인접하도록 배치하였으며, input-impedance boosting 목적으로 2개의 replica-DAC을 coupling capacitor의 앞에 배치시켰다. Prototype은 4.82μW의 낮은 전력소모와 183.4dB의 FoM<sub>SNDR</sub>\* 를 달성하였다.

Low-Cost Fast Tracking Technique

[그림 3] 본 논문에서 제안하는 Sensor readout frontend 구조

<sup>\*</sup>FoM<sub>SNDR</sub>=SNDR+10log<sub>10</sub>(BW/Power)

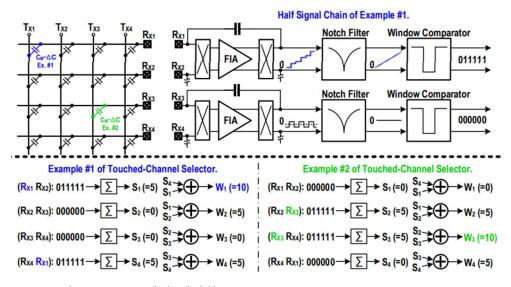

#12-3 은 Zhejiang<sup>1</sup> 대학에서 발표된 논문으로, Touch-sensor 의 정확성과 직결되는 높은 frame-rate 에 수반되는 dynamic power loss 의 감소 아이디어를 발표하였다. 높은 frame-rate 로 변하는 2-Level 0, 1 Digital 신호의 전압 변화( $\Delta V$ )를 3-level  $\Delta V$ /2 로의 변환을 통해  $CV^2f \rightarrow 1/4CV^2f$  로 감소시킨 dynamic power loss 가 큰 장점이다. 또한, 에너지 효율적인 터치 위치의 판단을 위해 스크린 전체를 탐색하지 않고, 터치된 부분과 인접한 부분의 신호 합  $S_{1,4}$ 을 정의하고 해당 신호의 합이 가장 큰( $W_1$ ) 신호에 공통된 신호( $R_{X1}$ )가 터치된 부분임을 결정하는 탐색 알고리즘을 사용해, dynamic power loss 를 크게 감소시켰다.

[그림 4] 본 논문에서 제안한 Energy-efficient Touch sensing algorithm

### 참고문헌

[1] N. Butzen et al., "Design of Single-Topology Continuously Scalable- Conversion-Ratio Switched-Capacitor DC-DC Converters," IEEE JSSC, vol. 54, no. 4, pp. 1039-1047, Apr. 2019.

#### 저자정보

#### 박수언 박사과정 대학원생

● 소속 : KAIST

● 연구분야 : Power Management IC 설계

이메일: tndjs12221@kaist.ac.kr홈페이지: https://icdesignlab.net

## 2025 IEEE CICC Review

서울대학교 전기정보공학부 박사과정 박현준

# Session 14 Innovations in High-Performance Analog and Mixed-Signal Circuit Design

최근 회로 및 시스템 분야에서는 고성능과 높은 효율성, 저잡음 특성을 동시에 만족하는 설계 기술이 주요 관심사로 떠오르고 있다. 2025 CICC Session 14에서는 최신 공정과 혁신적인 토폴로지를 활용하여 이러한 요구를 효과적으로 충족한 여러 연구가 소개되었다. 밀리미터파(mm-wave) VCO, MEMS 마이크로 스피커 드라이버, 초고속 다이내믹 비교기, 고정밀 오디오 디코더 등 다양한 응용 분야에서 성능과 효율성을 높이는 기술적 진보와 창의적인 접근법이 제시되었다.

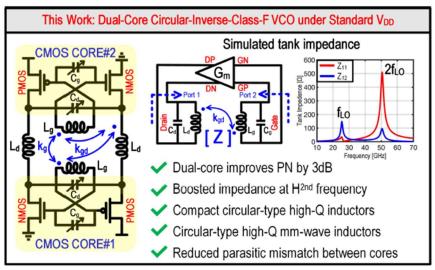

#14-1 본 논문은 65nm CMOS 공정에서 구현된 밀리미터파(mm-wave) 듀얼코어 circular-inverse-class-F VCO를 제안하였다. 기존 설계들이 FoM 향상을 위해 낮은 공급 전압을 요구하는 것과 달리, 본 설계는 표준 전압(1.2V) 하에서 우수한 성능을 제공한다. 22.0~28.4GHz의 주파수 대역에서 동작하며, 10MHz 오프셋에서 최대 192.2 dBc/Hz의 FoM과 206.2 dBc/Hz의 FoMA를 달성하였다. 특히, 듀얼코어 구성과 원형 토폴로지 인덕 터를 활용하여 위상잡음 성능을 약 3 dB 향상시키고, 칩 면적을 0.04 mm²로 최소화하였다.

[14-1] The proposed dual-core circular-inverse-class-F CMOS VCO.

#14-2 본 논문은 피에조 MEMS 마이크로 스피커(MMS)를 위한 고성능 클래스-H 드라이버를 제안하였다. 180nm BCD 공정으로 제작된 본 드라이버는 단일 리튬 이온 배터리 (2.75.5V)에서 구동되며, 최대 30Vpp의 오디오 신호 출력과 DC 바이어스 전압(515V)을 효율적으로 공급한다. Envelope tracking을 적용한 SIDO 부스트 컨버터와 클래스 AB 앰프를 통해 106.1dBA의 DR을 달성하였고, 디지털 및 아날로그 입력을 모두 지원하면서 2.1μs 이하의 매우 낮은 지연시간과 450μA의 낮은 idle 전류를 구현하였다.

[14-2] (좌)Block diagram of the MEMS micro-speaker driver

[14-3] (우)Proposed dynamic comparator with resistive dynamic bias pre-amplifier

#14-3 본 논문은 28nm FD-SOI 공정으로 제작된 저잡음, 고속의 다이내믹 비교기를 제안하였다. 제안된 비교기는 flying capacitor를 이용한 저항성 동적 바이어스 기법을 적용하여, 기존 비교기의 속도와 잡음 간의 트레이드오프를 극복하였다. 1GS/s 이상의 동작 속도에서 129μVrms의 낮은 입력 참조 잡음과 0.39ns의 짧은 CLK-Q 지연을 동시에 달성하였다. 또한 입력 공통 모드 전압(VCM)에 따른 잡음과 CLK-Q 지연의 민감도를 크게 낮추었으며, 소모 에너지는 변환 당 288fJ로 우수한 효율성을 나타냈다.

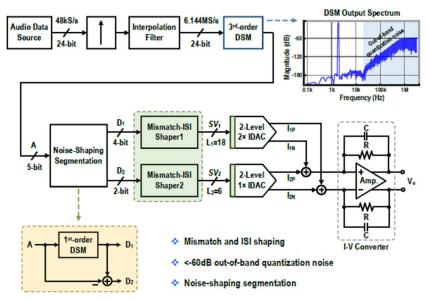

#14-4 본 논문은 mismatch와 ISI를 동시에 저감하는 단일 벡터 양자화기(VQ)를 활용한 고성능 IDAC 기반 오디오 디코더를 제안하였다. 0.18µm CMOS 공정으로 제작된 본 디코더는 mismatch와 ISI shaping 루프를 통합한 단일 VQ 기술을 통해 -117.1dB의 우수한 THD와 -107.4dB의 THD+N, 111.2dB의 DR(A-weighted)을 달성하였다. 특히, 620ps rms의 높은 클록 지터 조건에서도 -100.9dB의 낮은 THD+N을 유지하여 우수한 지터 내성을 보였으며, 효율적인 디지털 설계로 전력과 면적을 각각 23%와 22% 감소시켰다.

[14-4] Block diagram of the proposed audio decoder.

## 저자정보

## 박현준 박사과정 대학원생

소속 : 서울대학교연구분야 : 수학

● 이메일 : <u>spp098@snu.ac.kr</u>